版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

1、北京理工大學本科生畢業設計(論文)北京理工大學2012級電子技術課程設計數字定時控制器 第1章 概述1.1設計任務 設計一個具有數字鐘功能的數字定時控制器1.2設計要求 1、計時顯示范圍要求自00時00分00秒到23時59分59秒 2、具有校時功能,可對小時、分、秒分別進行校準3、要求預選時刻到達時被控對象連續響10秒,蜂鳴器在10秒內斷續鳴叫5次,即響1秒停1秒1.3設計目的 1、學習電子電路系統的設計方法和實驗方法 2、掌握EDA仿真設計工具的使用方法 3、培養學生獨立分析問題和解決問題的能力,為以后從事電子系統設計和開發應用打好基礎4、學會撰寫課程設計報告,為今后畢業設計及其報告撰寫做好

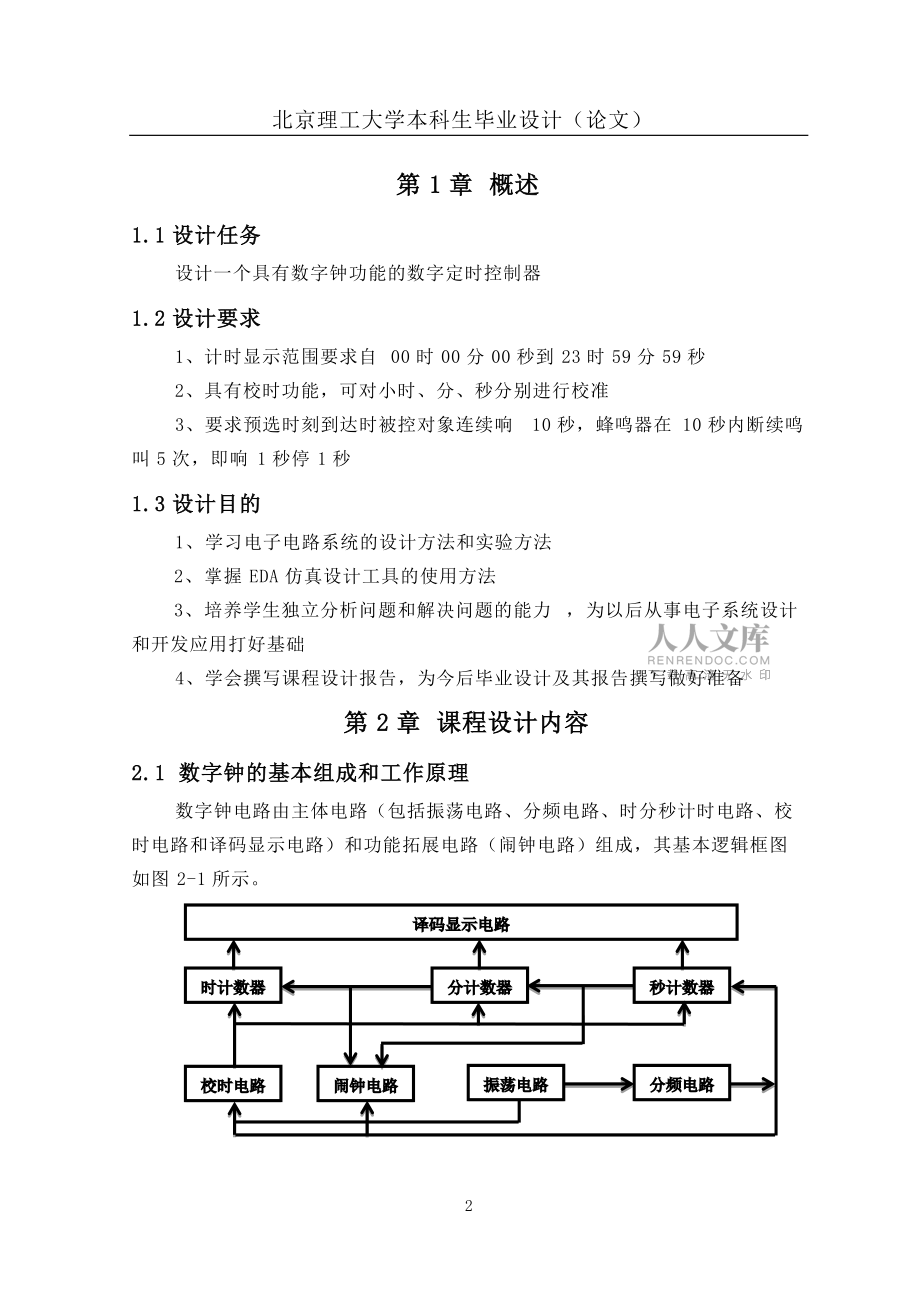

2、準備第2章 課程設計內容2.1 數字鐘的基本組成和工作原理譯碼顯示電路時計數器分計數器秒計數器校時電路鬧鐘電路分頻電路振蕩電路數字鐘電路由主體電路(包括振蕩電路、分頻電路、時分秒計時電路、校時電路和譯碼顯示電路)和功能拓展電路(鬧鐘電路)組成,其基本邏輯框圖如圖2-1所示。工作時,振蕩電路產生2HZ的方波信號,經分頻電路分頻后生成1HZ和0.5HZ的方波信號。其中,校時電路使用2HZ和1HZ的信號,計時電路使用1HZ的信號,鬧鐘電路使用0.5HZ的信號。秒、分、時計數器均使用2片74LS160搭建而成,秒、分計數器為60進制、時計數器為24進制。當秒計數器計數滿60時,輸出進位脈沖,送至分計數

3、器計數。當分計數器計數滿60時,輸出進位脈沖,送至時計數器計數。當時計數器計數滿24時,輸出清零脈沖,分別送至秒、分、時計數器的清零端完成清零,開始新一天的計時。2.2 各部分電路的設計與仿真2.2.1振蕩電路振蕩電路采用555計時器與RC組成的多諧振蕩電路,在multisim 12中直接使用電路向導即可搭建完成。結構如圖2-2圖2-2 555定時器RC振蕩電路電路搭建完成后,555定時器的out管腳即可輸出2HZ的方波信號。2.2.2分頻電路之前已經通過振蕩電路獲得2HZ的方波信號,設計中還需要1HZ和0.5HZ的方波信號,可通過1/2分頻器實現。本設計中采用74LS160作為分頻器,74L

4、S160是8421編碼的10進制計數器,將其功能設定為計數功能,把2HZ的信號輸出到CLK管腳,則其QA管腳便輸出1HZ的方波信號,QB管腳輸出0.5HZ的方波信號,仿真結果如圖2-3圖2-3 分頻電路2.2.3時、分、秒計時電路時、分、秒計時電路分別由2片74LS160組成。第一片74LS160(作為低位)的進位端(RCO管腳)接至第二片74LS160(作為高位)的時鐘端(CLK管腳),這樣兩片74LS160便組成了一個100進制的計數器。然后通過邏輯門電路譯碼,當高位160輸出為6(QDQCQBQA=0110)時,對高位160進行清零,便把100進制的計數器改造成了60進制,即可用于秒和分

5、的計數。對于時的計數,只需在門電路譯碼時稍作改變。當高位160輸出為2(QDQCQBQA=0010)且低位160輸出為4(QDQCQBQA=0100)時,對兩片160同時進行清零,便把100進制的計數器改造成了24進制的計數器。最后,只需把秒計數器的CLK端接1HZ方波信號,秒計數器的清零信號經非門后連接至分計數器的CLK端,同時分計數器的清零信號經過非門后連接至時計數器的CLK端,這樣便組成了一個計時時長為24小時的時鐘。仿真結果如圖2-4、圖2-5圖2-4 秒、分計數器(CLK端省略,秒計數器CLK接1HZ方波,分計數器CLK接秒計數器的進位信號)圖2-5 時計數器(CLK端省略,應接分計

6、數器的進位信號)2.2.4譯碼顯示電路譯碼顯示電路采用7段共陰極數碼管和其配套的譯碼芯片74LS248,使用時只需將74LS248的使能端接高電平,7個輸出端QAQG與數碼管的7個輸入端AG對應相連,4個輸入端ABCD與計時電路芯片74LS160的4個輸出端QAQD對應相接即可,仿真結果如圖2-6圖2-6 譯碼顯示電路(以秒計數器為例)2.2.5校時電路校時電路老師要求通過一個按鍵完成“計時-校時-校分-校秒-計時”的循環,于是本設計使用了移位寄存器CD4015,通過邏輯門電路使CD4015的輸出Q0Q1Q2Q3在“0000-1000-0100-0010-0001-0000”之間循環,共5個狀

7、態,如圖2-7所示。其中Q0Q1Q2Q3=0000代表暫停,Q0Q1Q2Q3=1000代表計時,Q0Q1Q2Q3=0100代表校時,Q0Q1Q2Q3=0010代表校分,Q0Q1Q2Q3=0001代表校秒。圖2-7 CD4015的5狀態循環接線圖要實現校時功能,應把CD4015對應的輸出Q0Q1Q2Q3=0100中的Q1與2HZ的校準信號相與、分計時器和Q0相與,兩者的結果在相或,最后連接到時計數器的CLK上。校分與校秒的原理類似,不再敘述。原理圖如圖2-8、2-9、2-10:CD4015的Q1CD4015的Q0分計時器進位信號時計時器CLK圖2-8 校時原理圖CD4015的Q2CD4015的Q

8、0秒計時器進位信號分計時器CLK圖2-9 校分原理圖CD4015的Q3秒計時器CLKCD4015的Q0圖2-10 校秒原理圖2.2.6鬧鐘電路 鬧鐘電路的要求是當到達預定時間時,蜂鳴器在10秒內斷續鳴叫5次,即響1秒停1秒,因此需要一個0.5HZ的方波信號,與預設時間的譯碼信號相與,相與的結果送至蜂鳴器。預設時間假設為7時5分,在把7時5分進行譯碼的同時再把秒計時器十位參與譯碼,這樣剛好能使譯碼有效時間為10秒,以滿足實驗要求。譯碼電路采用74LS138和邏輯門電路實現,原理如圖2-117時5分譯碼信號0.5HZ方波圖2-11 鬧鐘電路2.3 系統總體電路總體電路圖如圖2-12所示圖2-12

9、系統總體電路圖圖中,位于右下角的555定時器振蕩電路產生2HZ的方波信號,經74LS160分頻后得到1HZ和0.5HZ的信號,2HZ信號用于校時校分校秒,1HZ信號用于計時,0.5HZ信號用于鬧鐘。電路下方的開關用于控制CD4015的輸出,每次按下開關可以使數字鐘在“計時-校時-校分-校秒-暫停-計時”共5個狀態的循環中切換狀態。校時、校分、校秒的設計中采用與門鎖存進位信號,使得電路行使校準功能時不會發生進位,行使計時功能時才會進位。電路中間部分是由6片74LS160組成的計時電路,分為時、分、秒共3個計時器,每個計時器使用2片74LS160組成100進制計時器,然后通過邏輯門調整為24進制、

10、60進制、60進制的計數器用于計時、計分、計秒。計時部分的上面是7段共陰極數碼管和其配套的譯碼芯片74LS248。譯碼顯示電路與計時電路連接后便可以完成顯示功能。電路上方是鬧鐘譯碼電路,由74LS138和邏輯門組成。設計中使用了小時的個位十位、分鐘的個位十位、秒的十位共5位數參與譯碼,這樣譯碼有效的時間便為10秒。譯碼信號和0.5HZ信號相與,即可得到需要的鬧鐘信號。第3章 硬件實驗3.1 硬件實驗中遇到的問題在硬件實驗室中,老師告訴我們555定時器產生的方波脈沖是不穩定的,誤差很大,應該使用晶振來產生穩定的脈沖信號。在查閱資料后,我們修改了振蕩電路,使用32768HZ晶振來產生實驗所需的脈沖

11、信號。結果如圖3-1圖3-1 晶振產生的32768HZ信號設計時需要振蕩電路中產生2HZ的脈沖信號,那么便需要對32768HZ的信號進行分頻,我們采用了14 級二進制串行計數器CD4060來完成這個功能。CD4060的每一級分頻都是一個1/2分頻,那么經14級分頻后,便可獲得32768HZ/214=2HZ的信號,原理圖如圖3-2所示。圖3-2 晶振振蕩分頻電路(Multisim12中沒有CD4060,便用BD4060代替,實際實驗時使用的分頻器是CD4060)另外就是我們最初設計使用6個開關分別控制校時電路時分秒的個位十位,這個方案需要使用6片74LS160完成置數功能,需要的開關和芯片都很多

12、,不切合實際情況。這個方案被老師否決后,我們小組改用CD4015來完成實驗,這個方案只需要一個開關,即可完成“計時-校時-校分-校秒-暫停-計時”5狀態的循環。試驗中電路是分塊搭建,分別校驗功能后再組合起來。整個電路雖然很復雜,但分塊后每個模塊都比較簡單,易于搭建和差錯,除了一些小的接線錯誤外,沒有出現其他問題。圖3-3 硬件連線圖3.2 硬件實驗結果 根據仿真電路依次搭建計時、譯碼顯示、校時、鬧鐘、振蕩電路,分別檢測各部分電路功能,無誤后再把各個部分組合起來,最終按要求完成了數字電子鐘的設計,硬件連接如圖3-3(面包板左上為6片74LS160的計時模塊,左下為CD4015和邏輯門組成的校時模

13、塊,右上為74LS138和邏輯門組成的鬧鐘譯碼電路,右下為晶振和CD4060組成的振蕩電路。)3.2 硬件使用情況 如表3-1所示表3-1 硬件使用情況名稱數量74LS160774LS138474LS04274LS08374LS323CD40151CD4060132768HZ晶振120M電阻120PF電容2導線約300根第4章 課程設計的感想與總結這次課程設計是我在結束數電模電學習后,第一次使用數模電知識的任務。由于數模電知識的學習是在一兩個學期之前,這方面的知識已經有所遺忘,在最初設計方案和仿真時遇到了不小的困難。在選完題的一天里,我重新溫習了數電知識,熟知了一些常用芯片如74LS160、7

14、4LS161、CD4015、74LS248、74LS04、74LS08、74LS32等的使用方法,同時查閱數字鐘的相關資料,了解了數字鐘的基本構架和設計思路,最終完成了數字鐘的設計與仿真。硬件實驗過程中,主要的難度在于電路十分復雜,不易搭建、布線。另外便是最初方案555定時器被否決,重新使用晶振作為脈沖源,其他方面都比較順利。這次課程設計,從設計到仿真到硬件實驗再到最后撰寫報告,我的收獲頗多。設計與仿真過程讓我鞏固了數模電的相關知識,使我對課堂知識的應用的能力得到了進一步地提升。硬件實驗過程鍛煉了我的動手操作能力,豐富了我對于各個芯片的使用、排布、接線的經驗,最后的報告撰寫按照畢業設計報告的格式,為我未來完成畢業設計作了一個良好的鋪墊。最

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- 婚前簽婚后財產協議書

- 土石方運輸合同協議書

- 調換鋪面協議書

- 父親和親戚買房協議書

- 校園暴力和欺凌協議書

- 老公保證協議書

- 苗木成活協議書

- 職能授權協議書

- 美加談判協議書

- 炸雞店入股合同協議書

- DBJ41-T311-2025 《人民防空節鎳型不銹鋼防護設備選用與安裝技術標準》

- 2025-2030年中國軍用機器人行業市場現狀供需分析及投資評估規劃分析研究報告

- 2024年佛山市三水樂投控股有限公司招聘考試真題

- 新聞閱讀-2024年中考語文記敘文閱讀專項復習(原卷版)

- 2025-2030年電石項目投資價值分析報告

- 2025江蘇中天鋼鐵集團有限公司產品采購銷售合同

- 國家開放大學《Web開發基礎》形考任務實驗1-5參考答案

- 固體火箭發動機制造工藝

- 試卷密封線模板

- 廣告牌鋼結構設計計算書(共39頁).doc

- 外貿委托付款協議書模板(中英文版)

評論

0/150

提交評論