版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

1、2012 秋可編程邏輯器件課程設計報告報告題目:數字鐘實驗報告姓名學號郵箱成績組長組員.1 設計內容概述1.1功能概述 :一個具有計秒、計分、復位的數字鐘,數字鐘從0 開始計時,計滿 60 秒后自動清零,分鐘加 1,最大計時顯示 59 分 59 秒。用 A7 按鍵作為系統時鐘復位,復位后全部顯示 00 00 ,重新開始計時。1.2輸入輸出接口:NET "clk"LOC = "B8" NET "dula0"LOC = "L14" NET "dula1"LOC = "H12"NE

2、T "dula2"LOC = "N14" NET "dula3"LOC = "N11" NET "dula4"LOC = "P12"NET "dula5"LOC = "L13"NET "dula6"LOC = "M12" NET "dula7"LOC = "N13"NET "rst"LOC = "A7"NET &quo

3、t;wela0"LOC = "F12" NET "wela1"LOC = "J12"NET "wela2"LOC = "M13" NET "wela3"LOC = "K14"2 系統框圖及模塊劃分采用自頂向下分層設計思想的大概設計示意圖如下 :計時器秒計數分計數動態顯示60進制'.3 組員任務劃分1:負責本課題的開展,組織,協調及任務分配與安排問題,查找課題相關資料,完成主程序,及接口控制文件的編寫。2:完成分頻器模塊的程序編寫,以及最后

4、的報告整理。3:查找課題相關資料,參與子程序計數器模塊的編寫。4:完成數碼管部分程序的編寫,并完成程序的仿真及測試。4 各模塊詳細設計4.1模塊 1:分頻器4.1.1 功能:分頻器,能將高頻脈沖變換為低頻脈沖,它可由觸發器以及計數器來完成。由于一個觸發器就是一個二分頻器,N 個觸發器就是2N個分頻器。如果用計數器作分頻器,就要按進制數進行分頻。例如十進制計數器就是十分頻器, M進制計數器就為 M分頻器。 一般使用的石英晶體振蕩器頻率為 32768HZ,要想用該振蕩器得到一個頻率為 1HZ的秒脈沖信號,就需要用分頻器進行分頻,分頻器的個數為 2N=32768HZ,N =15即有 15 個分頻器。

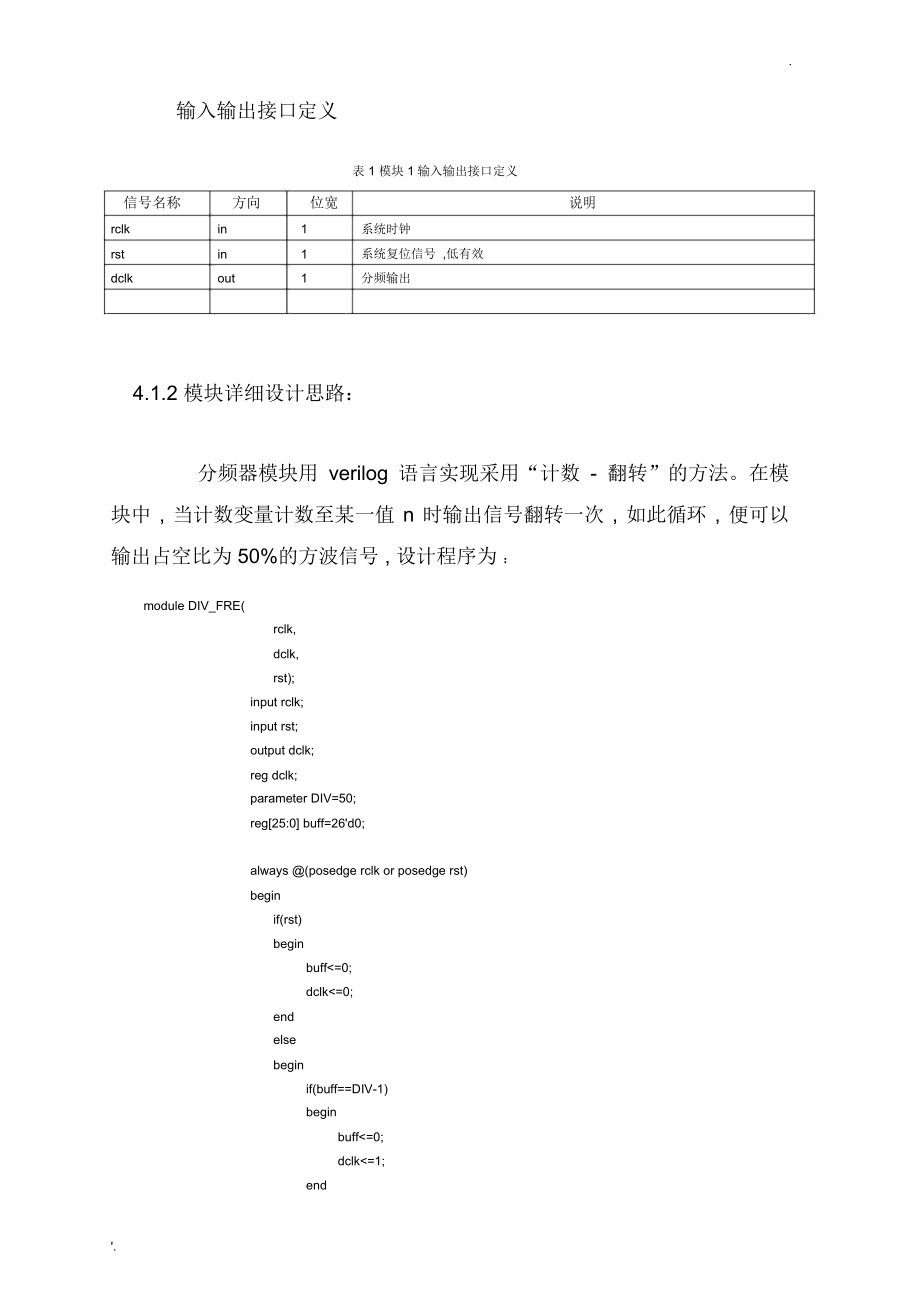

5、這樣就將一個頻率為32768HZ的振蕩信號降低為1HZ的計時信號,這樣就滿足了計時規律的需求:60 秒=1 分鐘, 60 分=1 小時。'.輸入輸出接口定義表 1 模塊 1 輸入輸出接口定義信號名稱方向位寬說明rclkin1系統時鐘rstin1系統復位信號 ,低有效dclkout1分頻輸出4.1.2 模塊詳細設計思路:分頻器模塊用 verilog 語言實現采用“計數 - 翻轉”的方法。在模塊中 , 當計數變量計數至某一值 n 時輸出信號翻轉一次 , 如此循環 , 便可以輸出占空比為 50%的方波信號 , 設計程序為 :module DIV_FRE(rclk,dclk,rst);inpu

6、t rclk;input rst;output dclk;reg dclk;parameter DIV=50;reg25:0 buff=26'd0;always (posedge rclk or posedge rst)beginif(rst)beginbuff<=0;dclk<=0;endelsebeginif(buff=DIV-1)beginbuff<=0;dclk<=1;end'.elsebegindclk<=0;buff<=buff+1;endendendEndmodule4.2模塊 2:計數器4.2.1 功能:4.2.2 計時器包括

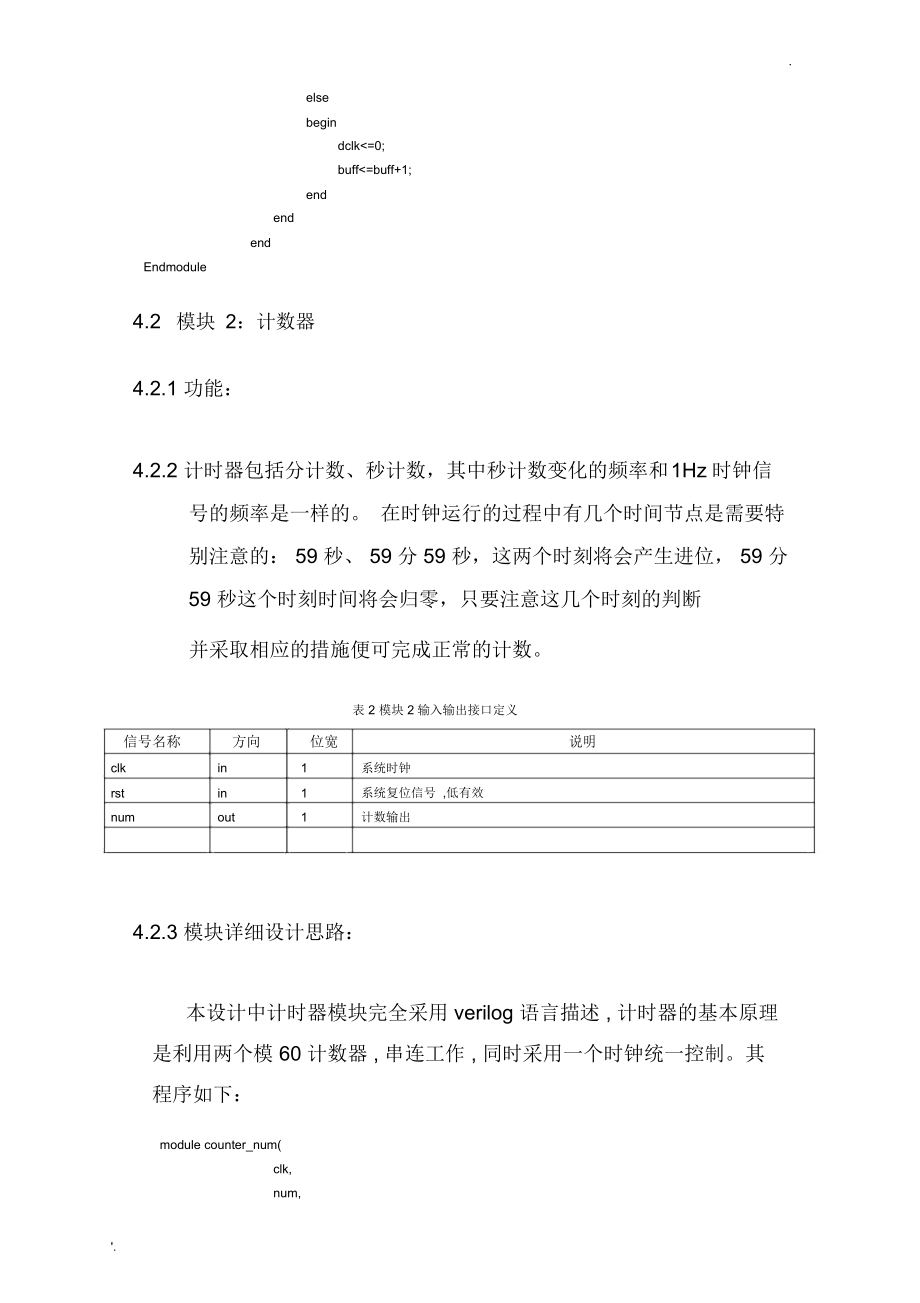

7、分計數、秒計數,其中秒計數變化的頻率和 1Hz時鐘信號的頻率是一樣的。 在時鐘運行的過程中有幾個時間節點是需要特別注意的: 59 秒、 59 分 59 秒,這兩個時刻將會產生進位, 59 分 59 秒這個時刻時間將會歸零,只要注意這幾個時刻的判斷并采取相應的措施便可完成正常的計數。表 2 模塊 2 輸入輸出接口定義信號名稱方向位寬說明clkin1系統時鐘rstin1系統復位信號 ,低有效numout1計數輸出4.2.3 模塊詳細設計思路:本設計中計時器模塊完全采用 verilog 語言描述 , 計時器的基本原理是利用兩個模 60 計數器 , 串連工作 , 同時采用一個時鐘統一控制。其程序如下:

8、module counter_num(clk,num,'.rst);input clk;input rst;output3:0 num;reg3:0 num=4'd0;parameter COUNTER=10;initialbeginnum=4'd0;endalways (posedge clk or posedge rst)beginif(rst)beginnum<=4'd0;endelsebeginif(num=COUNTER-1)num<=4'd0;elsenum<=num+1;endendEndmodule4.3模塊 3:數碼管

9、4.3.1 功能:動態顯示時間數據,前兩位表示分,后兩位表示秒。4.3.2設計思路:動態顯示 4 位數據時,需要一個 4 選 1 數據選擇器、一個 16 選 4 數據選擇器,和一個 7 段顯示譯碼器協調工作。 4 選 1 數據選擇器的作用是選擇點亮的數碼管, 16 選 4 數據選擇器的作用是選擇對應數碼'.管應該輸出的數據, 7 段顯示譯碼器的作用是對BCD碼進行譯碼, 便于數碼管顯示。分為控制部分和計數部分。控制模塊:module digit_num_fluid_display_4bit(clk,num0,num1,num2,num3,wela,dula,rst );input cl

10、k;input rst;input3:0 num0;input3:0 num1;input3:0 num2;input3:0 num3;output3:0 wela;output7:0 dula;wire3:0 num;reg3:0 num_buff;wire1:0 pos;reg1:0 pos_buff;reg1:0 i=2'b0;assign num=num_buff;assign pos=pos_buff;digit_led_display_1bit led_display (.clk(clk),.num(num),.pos(pos),.dula(dula),.wela(wela

11、) );always(posedge clk or posedge rst)beginif(rst)begini<=2'b00;'.pos_buff<=2'b00;num_buff<=0;endelsebegincase(i)2'b00:beginpos_buff<=2'b00;num_buff<=num0;end2'b01:beginpos_buff<=2'b01;num_buff<=num1;end2'b10:beginpos_buff<=2'b10;num_buff&l

12、t;=num2;end2'b11:beginpos_buff<=2'b11;num_buff<=num3;endendcasei<=i+1;endendendmodule計數模塊:module digit_led_display_1bit(/display digit led 1bitclk,/clk of refreshnum,/the num to displaypos,/the positiondula,/duan bianmawela);input clk;input3:0 num;input1:0 pos;output7:0 dula;output3

13、:0 wela;reg7:0 dula=8'b1111_1111;reg3:0 wela=4'b1111;parameter7:0 num_0=8'b1100_0000,'.num_1=8'b1111_1001,num_2=8'b1010_0100,num_3=8'b1011_0000,num_4=8'b1001_1001,num_5=8'b1001_0010,num_6=8'b1000_0010,num_7=8'b1111_1000,num_8=8'b1000_0000,num_9=8'b

14、1001_0000 ;always(posedge clk)begincase(pos)2'b00: wela<=4'b1110;2'b01: wela<=4'b1101;2'b10: wela<=4'b1011;2'b11: wela<=4'b0111;endcasecase(num)4'b0000: dula<=num_0;4'b0001: dula<=num_1;4'b0010: dula<=num_2;4'b0011: dula<=num_3;

15、4'b0100: dula<=num_4;4'b0101: dula<=num_5;4'b0110: dula<=num_6;4'b0111: dula<=num_7;4'b1000: dula<=num_8;4'b1001: dula<=num_9;endcaseendEndmodule5 仿真與測試及實驗結果:測試文件:module testclock;/ Inputs reg clk; reg rst;/ Outputs wire 7:0 dula; wire 3:0 wela;'./ Insta

16、ntiate the Unit Under Test (UUT)clock uut (.clk(clk),.dula(dula),.wela(wela),.rst(rst);initial begin/ Initialize Inputs clk = 0;rst = 1;/ Wait 100 ns for global reset to finish #100;rst = 1'b0;/ Add stimulus hereendalways #5 clk = clk;endmodule仿真時序圖:'.實驗結果:在實驗板上顯示如下 :59分 08秒:0分 1秒:'.18分

17、04秒:'.6 課程設計總結及設計心得通過本次設計,學習了 FPGA的知識,對 FPGA的應用有了一定的認識,本次設計的主要工作和成果如下1 、在學習了verilong語言的基礎上,能地運用verilong語言進行電路設計。2 、運用自頂向下的設計思想 , 對計時器各個功能模塊進行分解設計。3 、進行仿真驗證了整個模塊功能的正確性。4 、將各個模塊連接,組成一個系統,并在不斷調試中發現問題,并及時解決。5 、在實驗板上形成計時器的完整作品。個人心得:1 :在此次實驗的過程中我也有過挫折有不太清楚明了的地方,但是我并沒有氣餒,遇到困難我總是先自己尋找失敗的原因,仔細的檢查分析,請教同學、

18、請教老師。在這一過程中我對FPGA的掌握有了更進一步的見解, 我和我的組員分工合作,各自完成自己的模塊,大家相互學習,相互提高。我相信自己定能在以后的實驗課中能學到更多方面的知識,成為一個全面發展的學踐型學生。2:通過參加這次實驗,我學到了很多東西,首先我通過聽老師講述、查閱書本、網絡等多種渠道學習了FPGA的知識。在學習的過程中,我既體會到了學習的樂趣,又提高了合作能力,還懂得了對于我們在做事過'.程中發現的問題要冷靜的思考,不要盲目的進行。在這次設計過程中所得到的體會,在過去是沒有過的,在書本中是也是無法找到的。我以后將更努力的學習這方面的知識。3:在學習 FPGA的整個過程中,我建立起對FPGA學習的興趣,遇到困難時要勇于面對它,并想辦法解決。要對數字系統設計有比較全面的把握,如寄存器、內存、計數器、DSP等,盡力拓寬自己的知識面,比如數字電路、高速時鐘系統、電路工藝方面及系統設計等。結合具體項目進行設計開發應用,這樣才能有一個明確的進步方向。嘗試著從硬件

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- 中班班主任學期工作計劃范文(4篇)

- 施工材料購銷合同范本

- 線下體驗店服務協議

- 綠化行業技術交流協議

- 濕式除塵設備租賃合同(3篇)

- 和人合伙開店合同協議

- 次品蔬菜購銷合同協議

- 性勞動合同協議

- 樓頂廣告布合同協議

- 微信定制開發合同協議

- 美國加征關稅從多個角度全方位解讀關稅課件

- “皖南八校”2024-2025學年高一第二學期期中考試-英語(譯林版)及答案

- 一例脂肪液化切口的護理

- 定額〔2025〕1號文-關于發布2018版電力建設工程概預算定額2024年度價格水平調整的通知

- 【MOOC】機械原理-西北工業大學 中國大學慕課MOOC答案

- 一種基于STM32的智能門鎖系統的設計-畢業論文

- 煤礦安全監控系統設備管理報廢制度

- 機關事業單位退休人員養老金領取資格確認表

- 第五屆“國藥工程杯”全國大學生制藥工程設計競賽

- 柔性主動防護網分項工程質量檢驗評定表

- 中機2015~2016年消防系統維保養護年度總結報告

評論

0/150

提交評論