版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

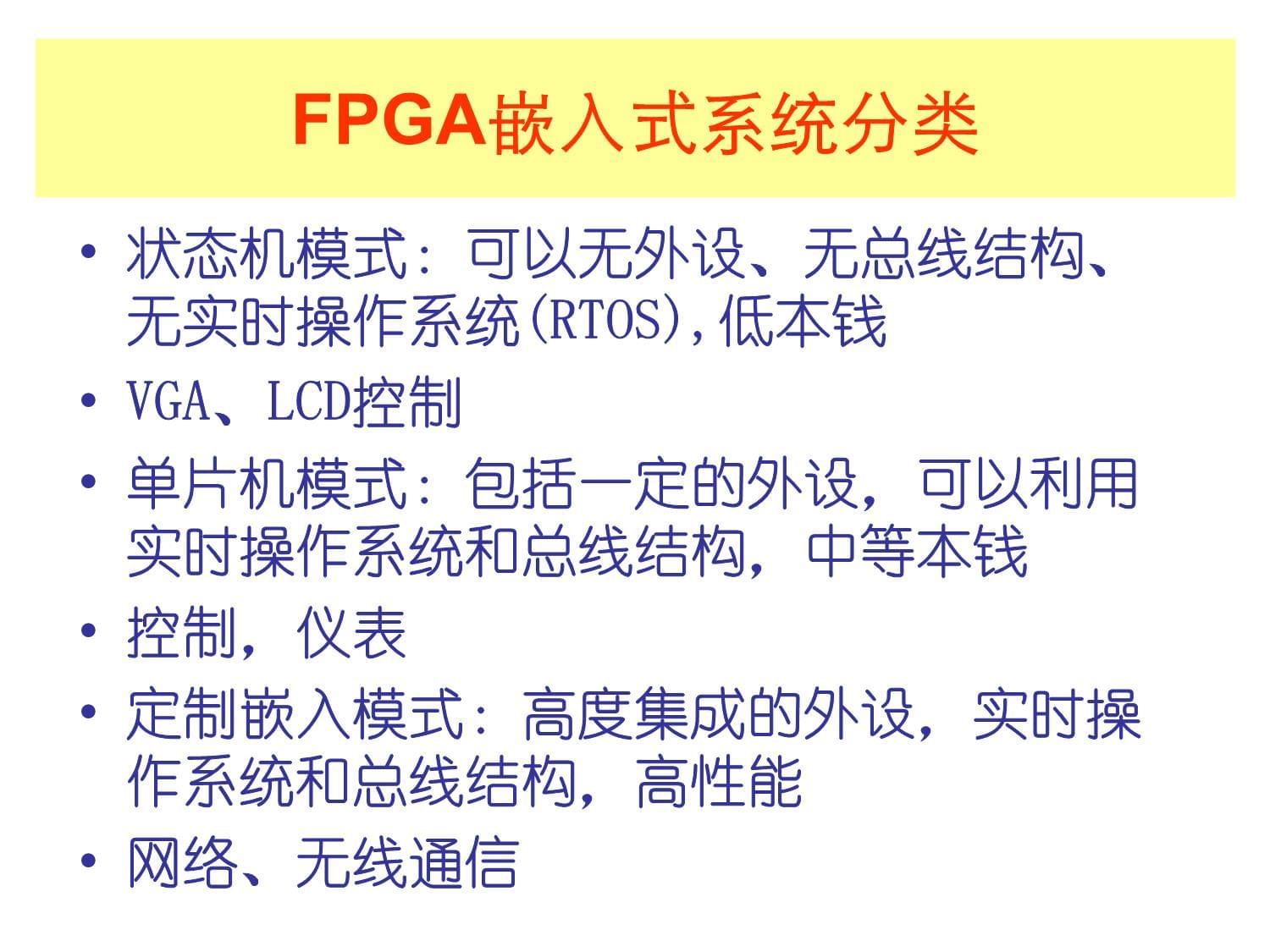

FPGA應用基于FPGA的嵌入式開發技術嵌入式系統概述以計算機技術為根底的專用應用系統,軟、硬件可剪裁CPU/DSP為核心硬件硬件固定,軟件可靈活配置基于FPGA的嵌入式系統軟硬件協同設計、工作硬件可編程SOPC〔片上可編程系統〕FPGA嵌入式系統分類狀態機模式:可以無外設、無總線結構、無實時操作系統(RTOS),低本錢VGA、LCD控制單片機模式:包括一定的外設,可以利用實時操作系統和總線結構,中等本錢控制,儀表定制嵌入模式:高度集成的外設,實時操作系統和總線結構,高性能網絡、無線通信采用90nm工藝后,FPGA器件:處理能力更強本錢降低、功耗少具備SOC規模和動態編程能力取代小批量ASIC和處理器FPGA嵌入式系統前景3類RISC處理器為核心PicoBlaze:8位軟核,支持匯編,程序駐留FPGA的塊RAMMicroBlaze:32位軟核,包含32個32位通用存放器和一個可選的32位移位存放器,時鐘達150MIPSPowerPC:32位PowerPC405硬核,程序級兼容PowerPC的嵌入式架構流行內核:MicroBlaze和PowerPCALtera公司:Nios,NiosIIXilinx公司嵌入式解決方案總體特征:32位微處理器CoreConnect外設總線支持CoreConnect總線的標準外設集合最精簡的和占用400個Slice片內微處理器軟核MicroBlazeMicroBlaze體系結構RISC架構:精簡指令系統哈佛結構:數據、指令32位雙總線(指令和數據總線)3級流水線32個通用存放器:R0~R31特殊存放器:PC(程序計數器),處理器狀態存放器(MSR)ALU,Shift,兩級中斷響應單元,3/5級流水線,桶形Shift內存管理/內存保護單元,浮點單元(FPU),高速緩存,異常調試和調試邏輯目前版本MicroBlazeV7.0MicroBlaze體系結構通用存放器:32個32位通用存放器R0~R31MicroBlaze編程模型寄存器名功能描述R0任何對R0的寫操作都被忽略R1~R13,R18~R31一般通用寄存器R14存儲中斷的返回地址R15位通用寄存器R16存儲跳轉的返回地址R17如MB配置為支持硬件異常,裝載硬件異常的返回地址,否則作通用寄存器使用特殊存放器程序計數器(PC)機器狀態存放器(MSR):處理器控制和狀態位指令集:32位指令,分A、B兩種類型,大致功能可分為邏輯運算、算術運算、分支、存儲器讀/寫、特殊指令等幾類A型:兩個源存放器,一個目的存放器,完成存放器到存放器的數據運算B型:一個源存放器,一個目的存放器和一個16位立即數,完成存放器和立即數之間的數據運算MicroBlaze編程模型CoreConnect:片上總線通信鏈帶字節允許的OPB(On-ChipPeripheralBus)V2.0:用于訪問低速外設高速LMB(LocalMemoryBus)接口:用于訪問片內高速存儲器FSL(快速簡單連接總線)主從設備接口:自定義IP與內部通用存放器的直接相連,用于訪問高速外設XCL(XilinxCacheLink)緩存接口:對片外存儲器的高速訪問MDM(MicroprocessorDebugModule)調試接口MicroBlaze總線接口高速總線DMA控制器多端口存儲控制器低速以太網MAC層處理器PCI/PCIe接口串口USB2.0Timer/PWMGPIOCAN/MOSTC/SPI其它MicroBlaze支持外設IPCore蘋果、IBM、摩托羅拉共同開發RISC架構PowerPC405:由IBM優化三個不同層面應用用戶指令集結構:UISA虛擬環境結構:VEA操作環境結構:OEA片內微處理器硬核PowerPC定義用戶級軟件所必須遵守的結構定義根本的用戶指令集、存放器、數據結構、浮點內存約定,及用戶程序異常處理模型、內存模型和編程模型所有PowerPC都遵守相同的UISA結構PowerPC3層結構(UISA)定義超級典型用戶軟件需求的附加用戶需求功能表述多個芯片訪問存儲器環境下的存儲器模型定義高速緩存模型及緩存控制指令集定義用戶角度基于時間的資源PowerPC3層結構(VEA)定義了典型的操作系統所要求的管理級資源定義內存管理模型、監控存放器、同步需求及異常模型定義了監控角度的基于時間的資源PowerPC3層結構(OEA)5級標量流水線哈佛結構,獨立指令緩存和數據緩存1個JTAG口TraceFIFO多個定時器一個內存管理單元(MMU)輔助處理器管理控制器(APU)分為通用存放器,專用存放器,機器狀態存放器,專用存放器,芯片控制存放器,基時存放器CoreConnect總線PowerPC體系結構PowerPC存放器表寄存器分類寄存器名讀寫權限功能描述通用寄存器R0~R31可讀可寫與內存數據交互機器狀態寄存器MSR可讀可寫機器工作狀態條件寄存器CR可讀可寫各種判決和跳轉的條件專用寄存器眾多部分可讀可寫,部分只可讀,部分只可寫操作PowerPC所有系統資源芯片控制寄存器DCR可讀可寫控制同一芯片內的其余外部處理器基時寄存器TRL,TBU只讀合成64位計數器5級標量流水線:取指、譯碼、執行、寫回、加載寫回指令分類:數學運算邏輯運算比較跳轉中斷指令PowerPC指令系統CoreConnect總線,以軟IP方式實現100MHz~133MHz的64位總線LMB和OPB總線,分別用來連接高速和低速外設PLB是高帶寬總線,64位數據總線寬度,別離地址、讀寫數據總線器件控制存放器總線,對外設器件存放器訪問PowerPC總線結構嵌入在EDK環境中的外設I/O設備中斷控制器設備定時器外部存儲器控制器以太網串口常用IP核及設備驅動嵌入在EDK環境中的外設I/O設備中斷控制器設備定時器外部存儲器控制器以太網串口常用IP核及設備驅動32位OPB總線外設,每位都可動態配置為I/O兩個通道,通過IPIF模塊與OPB總線相連存放器:32bit/16bit/8bit方式訪問,存放器是字邊界的(末尾地址2’b00)GPIO實現(硬件結構)OPB_IPIF接口GPIO_CORE接口OPBOPB_GPIOI/O通道I/O通道GPIO實現(軟件驅動)驅動軟件文件

xgpio.c,xgpio.h,xgpio_1.h,xgpio_i.h調用#include“xgpio.h”#include“xgpio_1.h”#include“xgpio_i.h”驅動函數 初始化:

XStatus

XGpio_Initialize(XGpio*InstancePtr,Xuint16DeviceId);

配置/查找:

XGpio_Config*XGpio_LookupConfig(Xuint16DeviceId);

數據方向設置:

voidXGpio_SetDataDirection(XGpio*InstancePtr,unsignedChannel);

讀入:

Xuint32XGpio_DiscreteRead(XGpio*InstancePtr,unsignedChannel);

輸出:

voidXGpio_DiscreteWrite(XGpio*InstancePtr,unsignedChannel,Xuint32Mask);嵌入式系統總線連接(MicroBlaze)嵌入式系統系統結構(MicroBlaze)0x0000_0000~0x0000_0017:特殊0x0000_0018~0xFFFF_FFFF:用戶地址LMB從0x0000_0018開始嵌入式系統總線連接(PowerPC)嵌入式系統結構(PowerPC)0xFFFF_FFFC:引導地址0xFFFF_0000~0xFFFF_FFFF:用戶空間Xilinx嵌入式開發工具集集成軟件環境ISE嵌入式開發套件EDK(EmbeddedDevelopmentKit)XPS(XilinxPlatformStudio):設計嵌入式處理器系統硬件的開發環境及GUI,完成嵌入式系統架構的創立、軟件代碼的編寫、編譯及FPGA芯片配置SDK(SoftwareDevelopmentKit):基于Eclipse,用于嵌入式軟件應用的開發和驗證,支持C/C++其它:用于Xilinx嵌入式處理器的硬IP;用于軟件開發的驅動和庫;在MicroBlaze和PowerPC處理器的C/C++軟件開發GNU編譯器、調試器;有關文檔和樣例程序Xilinx嵌入式開發流程硬件設計與調試軟件設計與調試ISEXPS軟件開發硬件開發驗證器件配置外部仿真器SDKXilinx嵌入式開發流程硬件邏輯創立硬件平臺:利用BSBWizard構建添加IPCore及用戶定制外設生成仿真系統并測試硬件生成硬件網表和Bit文件系統開發軟件系統:包括驅動軟件、庫、操作系統、應用軟件等,編譯生成.elf可執行文件合并軟硬件Bit文件下載配置在線調試EDKBit文件組成EDK文件管理框架板級支持包(BSP:BoardSupportPackage):針對硬件的設備驅動、庫等XMP文件:.xmp后綴,嵌入式工程工程文件,包括硬件結構描述文件(MHS)和軟件描述文件(MSS)指向、工程器件等MHS:硬件描述文件MSS:軟件描述文件UCF:約束文件CMD:批命令文件XPS根本操作啟動XilinxPlatformStudio直接由程序組工程運行ISE中EmbeddedProcessor創立新工程BSB(BaseSystemBuilder)向導定制XPS根本操作BaseSystemBuilderWizard選擇Project路徑和name(.xmp)CreateanewdesignCreatesystemfromacustomboard選擇FPGA器件類型和processor類型選擇時鐘、reset、片上存儲等增加并配置片外設備(GenericGPIO,UART)增加片內并配置片內設備選擇標準輸入/輸出(調試口),boot區設置自檢完成創立XPS根本操作工程信息面板系統組件面板控制臺輸出面板工程信息面板分頁工程:BSB向導中獲取,描述硬件設計工程文件:文本可翻開、編輯工程選項:翻開屬性窗口設置參考文件:XPS生成,不需要修改應用:軟件相關信息Boot:XPS自動生成,無需修改用戶應用軟件:處理器屬性,編譯器屬性,源代碼,庫文件IP目錄:列出了EDKIPCore和用戶定義IPCore,可以添加到系統中應用頁面SetCompilerOptions:設置編譯器屬性MarktoInitializeBRAMs:將軟件打包到初始化RAM中BuildProject:編譯,生成.elf可執行文件MakeprojectInactive:從初始化模塊中剔除GenerateLinkerScript:自動生成鏈接腳本系統組件面板分頁BusInterface:總線接口連接面板:表達設備接口與總線的連接,可以創立或刪除連接顯示區域:總線相聯設備接口Ports:端口Address:設備地址分配在XPS中添加IPCore選擇IPCatalog中IPCore,右鍵”AddIP”,或拖放到組件區配置總線接口,并連接總線模塊參數配置:模塊上右鍵/雙擊,選擇”ConfiggureIP”端口配置:內部/外部端口地址配置:在”Address”分頁中單擊”GenerateAddress”自動分配在XPS中定制用戶設備IP步驟:定制自定義IP添加到XPS工程中定制要求確定IP所需接口:連接總線(PLB,OPB)實現和驗證功能:將定制的用戶設備拷貝到正確目錄下,創立接口文件(MPD,PAO);參加到XPS的工程系統中IP接口模塊(IPIF)IPIF(IPinterface):預制的參數可調的接口模塊,同時提供一系列簡單總線協議;用戶設備可方便地實現與總線相連IPIC(IPinterconnect):用戶設備接口與定制邏輯之間的互連協議總線、IPIF、IPIC、用戶邏輯是上述實現用戶設備的環節IP接口模塊(IPIF)創立和導入設備CIP創立用戶設備步驟確定設備類型(四種):OPB從設備OPB主從結合設備PLB從設備PLB主從結合設備選擇菜單”Hardware“中”CreateorImportPeripheral”,建立/導入設備創立模板實現驗證導入XPS創立和導入設備創立和導入設備存放路徑創立和導入設備設備名及版本號創立和導入設備連接總線類型PLBFSLOPB創立和導入設備選擇IPIF效勞IPIF效勞機制根本從設備支持效勞S/WresetandMIR:生成RST,MIR兩存放器Userlogicinterruptsupport:中斷UserlogicS/Wregistersupport:可尋址存放器高級從設備支持效勞Bursttransactionsupport:突發傳送及緩沖FIFO:IPIF內建FIFO通路Userlogicaddressrangesupport:地址分段使能IPIF效勞機制中斷配置IPIF效勞機制軟件存放器設置IPIF效勞機制存放器和IP互連IPIF效勞機制定制IP仿真支持IPIF效勞機制模板語言選擇創立和導入設備完成IPIF配置后,生成IPCore框架文件軟件驅動:XPS工程文件drivers/IP目錄(my_led8_v1_00a)硬件結構:XPS工程文件pcores/IP目錄(my_led8_v1_00a)實現定制IP用戶局部邏輯:完成對總線信號的響應模板文件:XPS工程文件pcores/IP目錄(my_led8_v1_00a)下my_led8.vhd,user_logic.vhd,在此文件中定制邏輯修改MPD文件添加IPCore到XPS工程單擊”Hardware”菜單”CreateorImportPeripheral”項選擇需參加設備選擇HDL文件選擇mpd文件核查總線及信號配置存放器地址空間中斷配置IP和參數配置用戶端口屬性配置完成添加IPCore到XPS工程添加IPCore到XPS工程IP選擇添加IPCore到XPS工程語言選擇添加IPCore到XPS工程mpd文件選擇XPS高級操作軟件編譯系統仿真子系統設計(ISE/XPS協同)實現、下載在線調試XPS高級操作(軟件設計)EDK運行方式Standalone:裸CPU方式,簡單快捷,無法實現復雜功能OS:基于操作系統方式軟件應用文件類型(源文件)Xparameters.h頭文件.c/cpp源代碼.h頭文件.ld鏈接文件.s匯編文件xparameters.h實例本文件系統自動生成,定義了硬件系統的相關常量定義#defineXPAR_XGPIO_NUM_INSTANCES3#defineXPAR_LEDS_8BIT_BASEADDR0x40000000#defineXPAR_LEDS_8BIT_HIGHADDR0x4000FFFF#defineXPAR_LEDS_8BIT_DEVICE_ID0#defineXPAR_LEDS_8BIT_INTERRUPT_PRESENT0#defineXPAR_LEDS_8BIT_IS_DUAL0#defineXPAR_CPU_CORE_CLOCK_FREQ_HZ100000000軟件編譯設置編譯環境應用模式:可執行,調試輸出文件:.elf鏈接文件調試優化設置優化級別路徑設置庫搜索路徑頭文件搜索路徑鏈接庫編譯命令行軟件鏈接設置軟件鏈接設置Sections:段映射位置Heap,Stack:堆,堆棧Boot,Vector:引導段,中斷向量表Memory:顯示所有存儲信息Output:鏈接文件存儲位置EDK子系統設計背景FPGA設計是嵌入式處理器系統和其它定制邏輯的結合,利用ISE開發定制邏輯局部并實現頂層設計FPGA設計包括嵌入式處理器,用戶使用工程導航來實現,要允許使用ISE有關工具開發方式Top-down:直接添加EmbeddedProcessor源代碼Bottom-up:首先在XPS中開發嵌入式處理器設計,然后調用ISE添加該模塊Top-down開發流程ISE新建EmbeddedProcessor源代碼模板ISE自動調用EDK,開發有關嵌入式系統,生成網表ISE下單擊ViewHDLInstantiationTemplate,可看到處理器實例化EDK中修改C代碼后編譯后,只需在ISE中UpdateBitstreamwithProcessorDatabottom-up開發流程XPS創立嵌入式系統翻開ISE工程導航選擇Project->AddSource選擇XMP格式的XPS工程文件注意:ISE、XPS所選芯片型號相同XPS中的設計仿真概念:底層硬件模塊的仿真(由驅動程序)仿真類型:行為,結構,時序準備仿真庫:EDK、Xilinx仿真庫已經編譯XPS->Simulation->CompileSimulationLibraries準備仿真Bit文件:Compiler:編譯生成.elf文件,內含數據和代碼PlatGen:根據硬件設計生成.bmm文件,含塊RAM數據Data2MEM:根據上述文件,抽取數據代碼,system.v包含初始化存儲內容SimGen:生成仿真文件(選擇Simulation->GenerateSimulationHDLFiles),生成DO和V文件,產生仿真HDL模型文件EDK工具與流程SimulationGeneratorHardwarePlatformGenerationLibraryGenerationEmbeddedSoftwareDevelopmentISE

ToolsIPLibraryorUserRepositoryMSSLibGen.aCompiler(GCC).oLinker(GCC)ELFMHSPlatGenDrivers,

MDDMPD,PAOPCore

HDLSystemand

WrapperVHDsystem.BMMSynthesis(XST)NGCNGDBuildUCFNGDMAPNCD,PCFPARNCDBitGensystem.BITBitInitdownload.BITiMPACTsystem_BD.BMMSimGenBehavioral

VHDModelSimGenStructural

VHDModelSimGenTiming

VHDModelSimulationIPModelsISEModelsTestbench

StimulusCompEDKLibCompXLibApplication

Source

.c,.h,.sdownload.CMDEDKSW

Libraries編譯仿真庫XPS-Simulation->CompileSimulationLibrariesXilinx庫EDK庫仿真軟件支持SmartModel模式仿真模型生成SimGen操作來源文件MHS(MicroprocessorHardwareSpecification)文件system_name.v,peripheral_wrapper.vperipheral_wrapper.ngcsystem_name.ngcsystem_name.ncd產生目標文件system_name.vperipheral_wrapper.v其它工具與文件gcc編譯器生成system_name.elfPlatGen生成system_name.bmmData2MEM生成內存初始化模型system_name_init.v仿真模型生成(Data2MEM)Data2MEMsystem_init.[vhd|v]system.bmmexecutable.elfsystem.[vhd|v]仿真模型生成Hardware->GenerateNetlist:生成網表ProjectOptions->SimModel設為BEHAVIORALSimulation->GenerateSimulationHDLFiles:在simulation\behavioral目錄生成DO和Verilog文件XPS嵌入式系統實現流程綜合,產生硬件網表(Platgen):調用Hardware->GenerateNetlist生成硬件比特流文件Hardware->GenerateBitStream編譯應用程序選中工程,單擊鼠標右鍵,BuildProject配置FPGA芯片調用DeviceConfiguration->UpdateBitstream,將軟件、硬件比特流合并調用DeviceConfiguration->DownloadBitstream,下載編程固化嵌入式設計將.bit轉化成PROM配置文件添加Flash軟核控制器XPS嵌入式系統實現流程產生硬件網表(Platgen):綜合調用Hardware->GenerateNetlistXPS嵌入式系統實現流程生成硬件比特流文件:映射,布局,布線Hardware->GenerateBitStreamXPS嵌入式系統實現流程編譯軟件應用程序選中工程,單擊鼠標右鍵,BuildProject準備首先編譯XPS提供的庫函數生成鏈接腳本XPS嵌入式系統實現流程配置FPGA芯片調用DeviceConfiguration->UpdateBitstream,將軟件、硬件比特流合并調用DeviceConfiguration->DownloadBitstream,下載編程XPS嵌入式系統實現流程固化嵌入式設計將.bit轉化成PROM配置文件添加Flash軟核控制器FPGA片外連接SPI、BPI接口型Flash系統設計中添加相關接口硬件和驅動添加Flash驅動boot配置嵌入式系統調試XMD硬件調試ChipScopePro調試SDK軟件調試平臺綜合調試XMD在線硬件調試(PowerPC)XMD在線硬件調試(MicroBlaze)XMD調試方法建立工程連通硬件板編譯軟件工程,并下載選擇Debug->XMDDebugOptions,設置有關參數選擇Debug->LaunchXMD,啟動GDB效勞選擇Debug->LaunchSoftwareDebugger,顯示調試界面XMD在線硬件調試選擇Debug->XMDDebugOptions,設置有關參數調試方式調試硬件板上運行的程序使用周期精確指令設置仿真器的程序XMD在線硬件調試選擇Debug->LaunchXMD,啟動GDB效勞GDB效勞窗XMD在線硬件調試選擇Debug->LaunchSoftwareDebugger,顯示調試界面軟件調試窗口ChipScopePro調試工具ChipScope分析核都外掛在OPB/PLB總線上ChipScope_icon:連接JTAG和各監控核ChipScope_ila:監控自定義信號ChipScope_opb_iba:分析OPB總線ChipScope_plb_iba:分析PLB總線ChipScope_vio:不插入到網表中,使用JTAG采樣ChipScopePro調試工具例如添加、配置ChipScope_icon核IPCatalog頁->Debug類IP->AddIP,配置連接ChipScope_icon核端口添加、配置其它核ChipScope_ila核ChipScope_iba核…綜合、實現Hardware->GenerateNetlistHardware->GenerateBitstreamDeviceConfiguration->UpdateBitstream

XPSSDK調試工具XPSSDK調試工具基于EcilpseIDE功能版本管理工程管理,生成Makefile代碼編輯,錯誤導航調試在線搜索幫助信息與XMD集成Xilinx集成MicroBlaze,PowerPC編譯JavaVirtualMachinePlatformStudioSDKExtensionsC/C++DevelopmentPerspectiveEclipseplatformXPSSDK調試工具EclipseCDTXMDpowerpc-eabi-gdb(or)mb-gdbJTAG/XMDprotocolXilinxcustomgraphicaldebuginterfaceauto-launchedauto-launchedgdbremoteprotocolSDKDebugPerspectiveThestackframefortargetthreadsthatyouaredebugging.Eachthreadinyourprogramisrepresentedasanodein

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- 中學考試試題及答案

- 云南省賓川縣四校2025屆物理高二下期末經典模擬試題含解析

- 云南省宣威市第十中學2024-2025學年高二生物第二學期期末經典試題含解析

- 云南省綠春縣一中2025屆高二下物理期末復習檢測試題含解析

- 云南省施甸縣第三中學2025年生物高二下期末質量跟蹤監視試題含解析

- 車展場地租賃及品牌合作營銷合同范本

- 遺產繼承權轉讓與執行合同

- 城市綜合體安保服務合同

- 科技研發園區場地使用與研發人員勞動保障合同

- 餐飲連鎖退伙合同范本

- 建設工程法規考試題真題及答案

- 2024年江蘇省泰興市事業單位公開招聘教師崗考試題帶答案分析

- Q-GDW 10393.1-2024 變電站設計規范-第1部分:35kV變電站

- 2025-2030年中國磷酸行業市場現狀供需分析及投資評估規劃分析研究報告

- 2025年市場營銷專業人才考核試題及答案

- 防范惡劣天氣安全教育

- 分居協議(模版)

- 經鼻高流量吸氧在五官科麻醉氣道管理中應用專家共識(2025版)解讀

- 養老護理員考試模擬題與答案(附解析)

- 深圳市住房公積金管理中心員額人員招聘真題2024

- 2025年全國國家版圖知識競賽題庫及答案

評論

0/150

提交評論