版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

1、、基于3D集成電路的測試技術摘要:硅通孔技術,提供了高密度、低延時和低功耗的垂直互連,芯片在三維方向堆疊的密度大、互連線短,從而使三維堆疊芯片成為可能。文章介紹了基于TSVs的三維堆疊芯片新的測試流程TSVs綁定前測試的挑戰和TSVs綁定后的可靠性與測試挑戰.包括環形振蕩器、模擬退火法、MEMS探針和磁場成像技術,并且介紹了一種對于測試技術的優化方法。關鍵字:3D集成電路 硅通孔 測試技術Abstract:through-silicon vias(TSVs) technology provides high-density,low-latency and low-power vertical

2、interconnects through a thinned-down wafer substrate,thereby enabling the creation of three-dimensional stracked Ics(3D-ICs).The new 3D stracked chips test procedure based on TSVs,the challenge of pre-bond test and the reliability and test challenge of TSVs post-bond are described,including Ring Osc

3、illators,Simulated Annealing, ,MEMS Probing and Magnetic Field Imaging. And the paper introduces a optimization method for testing technology.Keywords: 3D-Ics through-silicon vias testing technology.第一章 引言盡管TSVs互連的三維芯片堆疊仍有許多技術挑戰,但其仍被視為是一種關鍵技術 以幫助半導體行業遵循摩爾定律到下一個10年。3D ICs利用快速、密集的片內通孔,克服了互連擴展的障礙。此外,3D

4、 ICs技術還使得芯片外形尺寸更加緊湊,從而實現真正意義上的SoC但為滿足該技術的高精度要求,需要對每一片IC進行電氣測試,以剔除有缺陷的部件,保證提供給用戶的產品質量。然而,3D技術的采用,受到了對3D測試問題認識不足和缺乏DFT技術的阻礙,其解決方案仍然未得到很好的研發,致使預期收益與使用價值之間存在較大的差距,因此在所有挑戰中3D ICs測試的工具和方法被視為頭號挑戰就不足為奇了。此外,三維芯片堆疊還存在一些特有的測試挑戰。1-51. 三維 IC 的優點三維 IC 具有比傳統二維 IC 更多的優點:(1) 互連線長度的縮短:與傳統的二維芯片設計相比較, 一個三維芯片比傳統的二維設計具有更

5、短的全局互連線長度。 這種全局互連線長的減少可明顯降低線延遲和功耗。前人研究工作指出,三維芯片結構可減少的布線長度為使用的芯片層數的平方根的一個因子。3 二維 IC 芯片薄化 TSV 連接三維 IC圖 1 三維集成電路的實現過程(2) 性能改進:因為減少了平均互連線長度,關鍵路徑的互聯長度也相應減少,可得到更高的三維 IC 性能,堆疊的帶寬也得到改善。一些學者的研究工作證明了三維芯片的這些優點。 三維算數部件設計證明了它的延遲優勢。 各種設計表明線長的減少使得三維算數單元設計可獲得約為 6-30%的延遲縮減。Intel 證實,通過以中度流水的連線為目標,當 Intel 奔四處理器被折疊到兩層三

6、維芯片中時, 流水的改變導致近 15%的性能的改進。三維緩存設計方面,由于互連主宰著緩存訪問延遲,而緩存訪問決定著微處理器的關鍵路徑,因而具有細粒度的三維劃分的三維緩存設計可縮短緩存訪問時間。(3) 降低功耗和能量:隨著制造技術的升級,芯片系統的總體功耗中互連功耗占的很大一部分。 線長的減少進而可節省三維 IC 設計的能量。 三維 Intel 實現中,由于全局互連減少,中繼器的數目和中繼鎖存器被減少 50%。這樣的三維堆疊重設計性能提高 15%,功耗降低15%。(4) 更高的內存帶寬:以 TSV 為中心的三維芯片技術可提供更高的內存帶寬, 因為 TSV 可提供 I/O 引腳之外的帶寬需求。 I

7、ntel 使用基線 Intel Core2 Duo 處理器研究了內存帶寬優點。有了堆疊內存,晶片上緩存容量增加了,性能改進了,減少了片外內存帶寬需求。(5) 異構堆疊:三維芯片技術可實現異構集成,因為不同層可被單獨制造, 然后堆疊起來。 在異構堆疊中, 每一層可有專門的電路類型如 RF、 模擬、 內存, MEMS、數字等。 一些學者開始考慮將非揮發性內存如電磁 RAM,或處理器頂上的變相內存堆疊起來,從而完成劃算的異構集成。(6) 更小的面積和降低的成本:三維芯片技術的一個明顯的優點為,晶元劃分可產生的較小面積。隨著技術升級和更高密度需求,微處理器的晶元尺寸逐漸增加。其結果是,制造產出受影響,

8、導致更高的制造成本。5-122. 三維 IC 的研究內容圖2,當前常見的 TSV 測試方法可分為綁定前測試和綁定后測試。綁定前測試檢測TSV是否在制造過程中產生缺陷, 而綁定后測試則檢測是否在綁定過程中引入新的TSV缺陷。相比綁定后測試, 綁定前測試更加困難。這是因為在綁定前如果此時晶片未薄化, TSV底端埋于襯底中, 限制了 TSV 的可觀察性; 而晶片薄化后, 雖然 TSV 底端露出, 但是 TSV 較小的間距和較高的密度使得探針測試單個 TSV 較困難. 鑒于探針測試單個TSV 較困難, Noia等提出利用一個探針同時測試多個TSVs 的測試方法, 該方法的主要缺點是探針卡需專門設計,

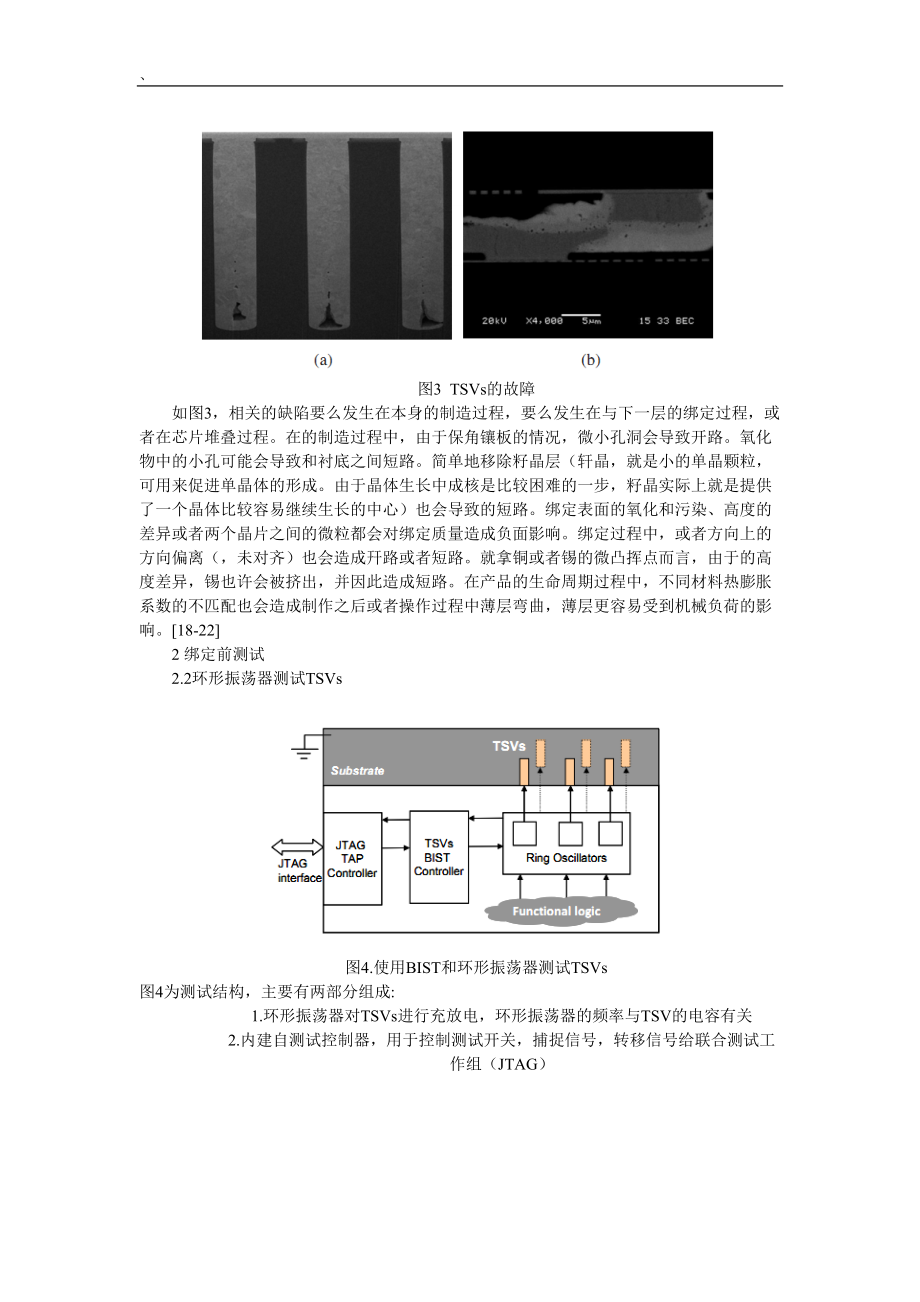

9、且過大的探針機械應力可能損壞本身無故障的TSV。Chen 等提出把 TSV 視為可充放電的 DRAM 單元, 利用敏感放大器來檢測 TSV 電容性缺陷, 該方法的主要缺點是需要模擬結構, 這種模擬結構在標準單元庫中不存在, 需人工設計. 葉靖等提出一種基于邊界掃描鏈的TSV測試方法, 該方法以少量面積開銷為代價換取測試時間的減小, 然而, 其主要用于測試TSV功能性故障而不是TSV電阻開路故障和泄漏故障。12-17圖2 常見3D Ics 測試流程第二章 TSVs測試方法1.TSVs的故障圖3 TSVs的故障如圖3,相關的缺陷要么發生在本身的制造過程,要么發生在與下一層的綁定過程,或者在芯片堆疊

10、過程。在的制造過程中,由于保角鑲板的情況,微小孔洞會導致開路。氧化物中的小孔可能會導致和襯底之間短路。簡單地移除籽晶層(軒晶,就是小的單晶顆粒,可用來促進單晶體的形成。由于晶體生長中成核是比較困難的一步,籽晶實際上就是提供了一個晶體比較容易繼續生長的中心)也會導致的短路。綁定表面的氧化和污染、高度的差異或者兩個晶片之間的微粒都會對綁定質量造成負面影響。綁定過程中,或者方向上的方向偏離(,未對齊)也會造成幵路或者短路。就拿銅或者錫的微凸揮點而言,由于的高度差異,錫也許會被擠出,并因此造成短路。在產品的生命周期過程中,不同材料熱膨脹系數的不匹配也會造成制作之后或者操作過程中薄層彎曲,薄層更容易受到

11、機械負荷的影響。18-222 綁定前測試2.2環形振蕩器測試TSVs 圖4.使用BIST和環形振蕩器測試TSVs圖4為測試結構,主要有兩部分組成:1.環形振蕩器對TSVs進行充放電,環形振蕩器的頻率與TSV的電容有關2.內建自測試控制器,用于控制測試開關,捕捉信號,轉移信號給聯合測試工作組(JTAG)圖5為環形振蕩器連接TSVs的測試結構環形振蕩器由一個環形逆變器逆變器組成,既能對TSVs進行測試,也能夠使振蕩器與TSVs斷開。該方法把TSV作為環形振蕩器的負載, 通過改變TSV驅動器的驅動強度測得 2 個不同的振蕩周期作為TSV特征, 把該特征與無故障的TSV特征比較判斷TSV是否存在故障。

12、23-262.2.2 對環形振蕩器進行改進Huang 等12提出利用環形振蕩器檢測TSV的電阻開路故障和泄漏故障, 該方法把TSV 作為環形振蕩器的負載, 通過改變TSV驅動器的驅動強度測得2個不同的振蕩周期作為 TSV 特征, 把該特征與無故障的TSV特征比較判斷TSV是否存在故障; 該方法的主要缺點是測試分辨率低, 并且能檢測的故障范圍有限。鑒于此, Deutsch 等提出采用多電壓測試 TSV, 該方法一定程度上提高了測試分辨率, 并擴大了故障檢測范圍. 然而, 該方法仍然存在 2 個問題: 1) 隨著被測 TSV 電容增大, 有故障和無故障的測試結果重疊度增大, 導致測試分辨率降低,

13、甚至無法分辨, 因此該方法不適于測試大電容 TSV。 2) 對 TSV 故障類型的診斷是基于如下的假設: TSV 只存在一種故障, 即要么只存在電阻開路故障要么只存在泄漏故障。 若將此假設條件放寬為TSV同時存在電阻開路故障和泄漏故障, 由于這 2 種故障對環形振蕩器周期有不同的影響, 會使得故障效應相互抵消或強故障掩蓋弱故障從而導致誤測或誤診斷。27-29 本文修改環形振蕩器, 把施密特觸發器引入綁定前TSV測試以測試大電容TSV,如圖6。另外, 相比電阻開路故障, 泄漏故障不但影響環形振蕩器的振蕩周期, 它還導致信號電壓衰減。基于此特性, 本文通過降低電源電壓使環形振蕩器不振蕩的方法檢測T

14、SV是否同時存在電阻開路故障和泄漏故障。30-34圖6 改良后的環形振蕩器2.3 晶圓探針測試TSVs 2.3.1 傳統的晶圓探針圖7.探針測試當前的探針技術使用懸臂或者垂直探針,最小間距是最多的探針數有幾千,有許多微小的標志,以達到良好的電氣接觸。這不足以探測直徑,孔徑的尖端。可能會有幾千個,都用易碎的銅構成,在相同表面經不住下層內置的微小標志的銅與銅綁定。探測銅與錫的微凸傳點也是一個挑戰,不過稍微容易一點,因為微凸揮點的大小和間距更大,那么微凸輝點的數量就更少,受到微小標志的限制也就更低。對于綁定前晶片測試,圖7我們區分出底部晶片和其他非底部晶片。底部晶片有綁定金屬絲或者倒裝芯片襯塾用于與

15、外部連接。這些襯塾提供了當前探針技術可探測的接口。然而,對于非底層晶片,情況就不同了。它們只從連接接收所有的功能信號(功率、接地、時鐘、控制、數據)。這些尖端和襯塾對當前的探針技術來說都太密集、太微小和太脆弱了。35-372.3.2 MEMS探針 為了解決傳統探針在與TSVs接觸時可能會對其造成損傷,因此提出了一種新型MEMS探針,如圖8(a)。采用銅鈹合金,其具有較高的強度和無磁性。其中接觸探頭的尺寸為5m*5m,兩側為懸梁,探針通過與TSVs表面進行短暫的電學接觸,通過兩側的梁保持平衡,通過檢測證明探針中央的壓力為0,圖8(b)能夠很好的減少TSVs損傷。38-43 a b圖8 MEMS探

16、針結構探針的設計有以下要求: 1.表面平坦光滑,增大接觸表面,較小接觸電阻 2.有限的接觸力較少對TSVS表面造成的損傷 3.足夠大的接觸面積與TSVs表面適配44-453.綁定后測試由于TSVs在綁定前不能進行邏輯訪問,因此在綁定前測試組合邏輯電路是非常困難的,為了提高可測性和,提出了一種包裝單元(WC)加到TSVs的兩端。 Fig.9. IEEE Standard WCFig. 10. Reusing an existing op for both controlling the FO cone of an inbound TSV and observing the value on th

17、e TSV. 上圖為加入多路復用器的測試電路,當獲取行斷開時,掃描觸發器會捕捉來自TSVs行的信號,否則,會捕捉扇入電路的輸出信號,這種設計不會與普通模式發生干擾。46-474 測試技術的優化 由于3D集成電路的大功率密度,會導致在測試中溫度的過高,并且由于成本問題沒有散熱裝置,可能會導致測試的不準確。因此提出了一種熱感測試調度,使集成電路的溫度低于溫度界限,雖然增加了測試時間。但卻能降低測試期間溫度,從而提高測試的準確率。 在優化過程中,通過一個簡單的熱阻模型,通過熱采集模擬程序(Hotspot)推算出電路的最大承受溫度,從而使測試過程中溫度低于最高溫度限制。48-50圖9 測試流程第三章

18、總結 本文首先介紹了3D集成電路的測試過程,并詳細講述了幾種綁定前后TSVs的測試技術,并介紹了一種熱阻模型,其中綁定前TSV測試能在較早的制造流中排除有故障的TSV,熱阻模型能夠提高測試準確率,如果能夠將其結合起來,從能夠有效的提高產品良率。參考文獻:1 商進,集成電路低功耗測試技術研究進展,科技論壇,J,2009,082 K. H. Lu, et al. Thermo-Mechanical Reliability of 3-D ICs Containing Through Silicon ViasC. IEEE conference of Electronic Components and

19、 Technology. 2009.3 S.-K. Ryu, et al. Impact of Near-Surface Thermal Stresses on Interfacial Reliability of Through-Silicon-Vias for 3-D InterconnectsJ. IEEE Transactions on Device and Material Reliability, 2010.4 K. H. Lu, et al. Thermal Stress Induced Delamination of Through Silicon Vias in 3-D In

20、terconnectsC. IEEE Conference of Electronic Components and Technology, 2010.5 B. Noia and K. Chakrabarty, Pre-bond probing of TSVs in 3D stacked ICs, in Proc. ITC, 2011, pp.1-10. 6 Y. Lou, Z. Yan, F. Zhang, and P.D. Franzon, Comparing ThroughSilicon-Via (TSV) Void/Pinhole Defect Self-Test Methods,pr

21、esented at J. Electronic Testing, 2012, pp.27-38. 7 Yuan Chen, Cheng-Wen Wu, Ding-Ming Kwai On-Chip TSV Testing for 3D IC before Bonding Using Sense Amplification, in proceedings of ATS 2009. 8 Tsai M, Klooz A, Leonard A, Appel J, Franzon P, Through silicon via (TSV) defect/pinhole self test circuit

22、 for 3D-IC, in proceedings of 3DIC, 2009. 9 Sergej Deutsch and Krishnendu Chakrabarty, Non-Invasive Pre-Bond TSV Test Using Ring Oscillators and Multiple Voltage Levels, in Proc DATE2013, pp 1065-1070 10 Gabriel H. Loh, Yuan Xie, and Bryan Black. Processor Design in 3D Die-StackingTechnologies. IEEE

23、 Micro, 27(3):3148, May/June 2007. 11 Shamik Das, Anantha Chandrakasan, and Rafael Reif. Design Tools for 3-D Integrated Circuits. In Asia South Pacic Design Automation Conference (ASP-DAC), pages 5356, 2003.12 Moore GE, Intel. Cramming more components onto integrated circuits. Electronics (April 19

24、, 1965); 38(8): reproduced in Proc. IEEE, (1998); 86(82).13 Erik Jan Marinissen, Testing TSV-Based Three-Dimensional Stacked IcsJ, EDAA 978-3-9810801-6-2/DATE10 2010.14 Infante F, CNES, Perdu P, CNES, Lewis D, IMS Laboratories. Magnetic microscopy for 3D devices: defect localization with high resolu

25、tion and long working distance on complex system in package. ESREF; 2009.15 Dean L. Lewis and Hsien-Hsin S. Lee. A Scan-Island Based Design Enabling Pre-bond Testability in Die-Stacked Microprocessors. In IEEE International Test Conference (ITC), October 2007.16 Vallett David P, IBM, Smith Christian

26、, Altman Frank, Fraunhofer-Institute. Enhanced comparison of lock-in thermography and magnetic microscopy for 3D defect localization in system in packages. ISTFA proceedings; 2012.17 Knauss LA, Frazier BM, Christen HM, Silliman SD, Harshavardhan KS, Neocera, Fleet EF, et al. University of Maryland.

27、In: Mahanpour M, Ghaemmaghami A, AMD, editors. Detecting power shorts from front and backside of IC packages using scanning SQUID microscopy. ISTFA Proceedings; 1999.18 Knauss LA, Frazier BM, Cawthorne AB, Neocera, Budiarto E, Crandall R, Melnik S, Bennett C, Intel. Backside fault isolation using a

28、magnetic-field imaging system on SRAMs with indirect shorts. ISTFA proceedings; 2000.19 Gaudestad J, Talanov V, Neocera, Huang PC, TSMC. Space domain reflectometry for opens detection location in micro bumps. ESREF; 2012.20 Wu X, Chen Y, Chakrabarty K, Xie Y (2008) Test-access mechanism optimization

29、 for core-based three-dimensional SOCs. In: IEEE international conference on computer de-sign, pp 212218. 21 Gaudestad J, Talanov V, Orozco A, Neocera, LLC, Khai Ling Khoo, Altera. Open localization on copper wirebond using space domain reflectometry copper wirebond reliability. IRPS; 2013.22 Fleet

30、EF. PhD dissertation. Design and applications of a cryo-cooled scanning SQUID microscope. College Park: University of Maryland; 2000.23 Robert S. Patti. Three-Dimensional Integrated Circuits and the Future of System-on-Chip Designs. Proceedings of the IEEE, 94(6):12141224, June 2006.24 Crepel O, Poi

31、rer P, Descamps P, LaMIP Philips Semiconductor. Magnetic microscope for ICs failure analysis: comparative case studies using SQUID, GMR and MTJ systems. IPFA proceedings; 2004.25 Gaudestad J, Orozco A, Talanov V, Huang Neocera PC, TSMC. Open failure detection in 3D device non destructively. LSI Test

32、ing Symposium; 2012.26 Vallett David P, IBM Systems & Technology Group, Essex Junction, VT, USA. A comparison of lock-in thermography and magnetic current imaging for localizing buried short-circuits. ISTFA proceedings; 2011. 27 J. W. Joyner, P. Zarkesh-Ha, J. A. Davis, and J. D. Meindl, “A threedim

33、ensional stochastic wire-length distribution for variable separation of strata,” in Proc. IEEE Int. Interconn. Technol. Conf., Burlingame, CA, Jun. 2000, pp. 126128.28 C. Ababei, Y. Feng, B. Goplen, H. Mogal, T. Zhang, K. Bazargan, and S. Sapatnekar, “Placement and routing in 3D integrated circuits,

34、” IEEE Design Test. Comput., vol. 22, no. 6, pp. 520531, Nov.Dec. 2005.29 W. R. Davis, J. Wilson, S. Mick, J. Xu, H. Hua, C. Mineo, A. M. Sule, M. Steer, and P. D. Franzon, “Demystifying 3D ICs: The pros and cons of going vertical,” IEEE Design Test. Comput., vol. 22, no. 6, pp. 498510, Nov.Dec. 200

35、5.30 Y. Xie and Y. Ma, “Design space exploration for 3D integrated circuits,” in Proc. 9th Int. Conf. Solid-State Integr.-Circuit Technol., Beijing, China, 2008, pp. 23172320.31 B. Noia, K. Chakrabarty, and E. J. Marinissen, “Optimization methods for post-bond die-internal/external testing in 3D sta

36、cked ICs,” in Proc. IEEE Int. Test Conf., Austin, TX, Nov. 2010, pp. 19.32 X. Wu, P. Falkenstern, K. Chakrabarty, and Y. Xie, “Scan-chain design and optimization for three-dimensional integrated circuits,” ACM J. Emerg. Technol. Comput. Syst., vol. 5, no. 2, pp. 126, Jul.33 K. Banerjee et al., “3-D

37、ICs: A novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration,” Proc. IEEE, vol. 89, no. 5, pp. 602633, May 2001.34 U. Kang et al., “8 Gb 3-D DDR3 DRAM using through-silicon-via technology,” IEEE J. Solid-State Circuits, vol. 45, no. 1, pp. 111119

38、, Jan. 2010.35張鷹,梁華國,常郝,基于環形振蕩器的綁定前硅通孔測試,計算機輔助設計與圖形學學報,J.2015,1136 M. Jung, et al. TSV Stress-aware Full-Chip Mechanical Reliability Analysis and Optimization for 3D IC. C Proceedings of ACM Design Automation Conference, 2011.37 韓博宇,王偉,劉坤,陳田,李潤豐,基于TSV的3D堆疊集成電路的測試J,合肥工業大學學報,2014,438 徐本柱,變結構工序狀態網的模型與算

39、法研究D.合肥合肥工業大學,201139 Abbau M, Cheng K-T, Furukawa Y, Komatsu S, Asada K. Signature-based testing fordigitally-assisted adaptive equalizers in high-speed serial links. European Test Symposium, 2009, 107112.40 周建民,應用硅穿孔技術的3D集成電路D,應用專題,2014,10.41 Nabeeh Kandalaft, Testing 3-D IC Through-Silicon-Vias(TSVs) by Direct ProbingJ, IEEE transactions on very large scale intrgration systerm, VOL. 32, NO. 4, APRIL 2013.4

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- 明星代言活動獨家代理經紀協議

- 建筑智能化設備采購與智能監控系統服務協議

- 2025公寓租賃合同范本 房屋租賃合同

- 2025健身房轉讓合同書

- 腫瘤患者的飲食管理

- 醫學生實驗室安全

- 績效考核的流程和方法

- 人教版小學語文一年級下冊第五單元試題

- 2025年交通安全知識試題

- 小學數學2025年課程標準解讀心得體會模版

- 設備購買合同模板示例

- 基于JAVA的寵物管理系統實現畢業論文

- 2024年小區地下車位租賃合同

- 2022-2023學年上海市閔行區八年級(下)期末數學試卷

- 專題03 陜西省(A卷)-2022-2023年各地中考英語聽力真題合集(含聽力原文及MP3)

- 諾如病毒校園防控知識

- 常見神經系統疾病康復15節

- 關于梳理、修訂、完善公司規章制度的通知

- 會計信息考試系統復習題(試題及答案)

- 高中物理學習中的數字化教學資源

- (高清版)TDT 1067-2021 不動產登記數據整合建庫技術規范

評論

0/150

提交評論